晶振不封装进芯片内部的原因分析

扫描二维码

随时随地手机看文章

在电子设备中,一些应用需要高度稳定的交流信号,对频率的精确控制十分关键。传统上,LC振荡器被广泛用于生成这样的信号。然而,LC振荡器的稳定性较差,容易受到环境温度、电源变化等因素的影响,导致频率漂移。为了解决这一问题,发展出了一种基于石英晶体的振荡器,即晶体振荡器,可以产生高度稳定的信号。但奇怪的是,尽管现代芯片制造技术已经非常先进,但我们很少见到晶振被内置到芯片中的情况。那么,为什么晶振没有内置到芯片中呢?

实用性和成本

首先,在过去的几十年里,芯片制作工艺可能还无法将晶振直接集成到芯片的内部。然而,随着技术的进步,现代的芯片制造工艺已经可以实现晶振的内置。那么,为什么不这样做呢?

一方面,有些应用并不需要非常高度稳定的信号频率,对于这些应用来说,内置晶振会增加成本,而且没有太多的实际效益。另一方面,即使应用需要高度稳定的信号频率,外部的晶振也可以通过封装在芯片旁边或者与芯片相连的方式来提供。

材料限制和成本考虑

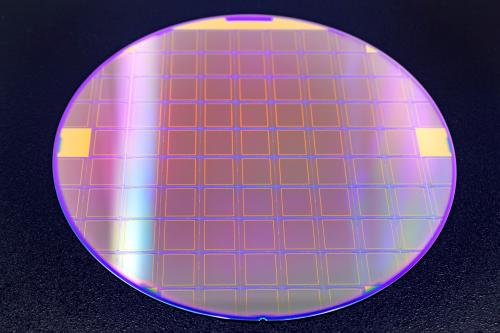

芯片的主要材料是硅,而晶体振荡器使用的是石英晶体。这两种材料无法直接结合在一起,但可以通过封装在一起的方式解决。然而,这样做会增加成本和复杂性,因为封装过程需要额外的工序和材料。

此外,石英晶体的制造成本相对较高,如果将晶振直接内置到每个芯片中,无论应用需要多大的精确性和稳定性,都会增加芯片的成本。相比之下,将晶振作为一个独立的元件,可以根据具体需求选择合适的晶振,更经济实惠。

频率灵活性和电路设计

将晶振内置到芯片中会限制其频率。一旦内置,频率就固定不变,无法更换晶振以提供不同的频率。然而,将晶振放在芯片外部,可以根据需要自由选择不同频率的晶振。这对于一些应用来说非常重要,比如需要在不同频率下运行的系统或者需要频率可调的系统。

此外,将晶振作为独立的元件,可以简化芯片的电路设计和布局。在芯片设计中,需要考虑到与晶振相关的布线和引脚,以确保信号的传输质量和稳定性。而将晶振作为一个独立的元件,可以让芯片的设计更加灵活,布局更加紧凑。

尽管技术已经允许晶振内置到芯片中,但实际上,由于实用性、成本、材料限制以及频率灵活性等因素的权衡,晶振仍然很少内置到芯片中。与其内置晶振,现代芯片更倾向于提供丰富的时钟和频率控制选项,以满足不同应用的需求。通过外部晶振的使用,我们可以根据需要选择合适的频率,并保持系统的稳定性和灵活性。因此,晶振没有内置到芯片中并不意味着技术的不足,而是一种基于实际需求和成本效益的选择。

原因1、早些年,芯片的生产制作工艺也许还不能够将晶振做进芯片内部,但是现在可以了。这个问题主要还是实用性和成本决定的。

原因2、芯片和晶振的材料是不同的,芯片 (集成电路) 的材料是硅,而晶体则是石英 (二氧化硅),没法做在一起,但是可以封装在一起,目前已经可以实现了,但是成本就比较高了。

原因3、晶振一旦封装进芯片内部, 频率也固定死了,想再更换频率的话,基本也是不可能的了,而放在外面, 就可以自由的更换晶振来给芯片提供不同的频率。有人说,芯片内部有 PLL,管它晶振频率是多少,用 PLL 倍频/分频不就可以了,那么这有回到成本的问题上来了,100M 的晶振集成到芯片里, 但我用不了那么高的频率,我只想用 10M 的频率, 那我为何要去买你集成了 100M 晶振的芯片呢, 又贵又浪费。

我们通常所说的 "片内时钟", 是不是实际上片内根本没有晶振, 是有RC 振荡电路。

由图可以看出系统时钟的供给可以有3种方式,HSI,HSE,PLL。如果选用内部时钟作为系统时钟,其倍频达不到72Mhz,最多也就8Mhz/2*16 = 64Mhz。